Logic Voltage Level

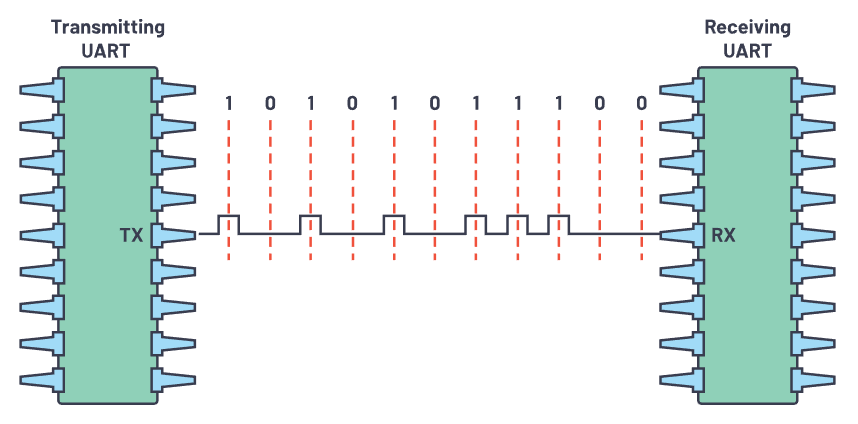

การออกแบบวงจรนั้นจะต้องคำนึงถึง Logic Voltage Level เพื่อให้สัญญาณที่สื่อสารกันของแต่ละ IC ไม่ผิดพลาด โดยจะแบ่งชนิด Input และ Output ดังนี้ TTL และ CMOS ปกติแล้วเราจะมองสัญญาณเป็น 2 สถานะคือ สถานะ High (1) และสถานะ Low (0) ตัวอย่างเช่นสัญญาณ UART ในรูปด้านล่าง สมมติว่าวงจรนี้ใช้แรงดัน 5V ถ้าสัญญาณมีแรงดัน 5V จะเป็นสถานะ High และถ้าแรงดันเป็น 0V จะเป็นสถานะ Low ก่อนไปหัวข้อถัดไป อยากแนะนำให้รู้จักคำศัพท์ต่อไปนี้เสียก่อน

- Voltage Input High (VIH) : ช่วงแรงดันที่ IC คอนเฟิร์มว่าเป็นสถานะ High

- Voltage Input Low (VIL) : ช่วงแรงดันที่ IC คอนเฟิร์มว่าเป็นสถานะ Low

- Voltage Output High (VOH) : ช่วงแรงดันที่ IC ปล่อยสถานะ High

- Voltage Output Low (VOL) : ช่วงแรงดันที่ IC ปล่อยสถานะ Low

TTL Voltage Level

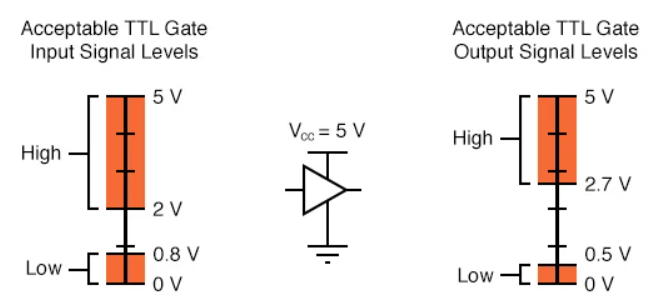

โดยปกติแล้ว Output ของ TTL จะปล่อยแรงดันได้ไม่ดีตามที่คาดหวัง เช่น ระดับแรงดัน 5V แต่อาจจะจ่ายออกไปจริงๆแค่ 4V ในรูปด้านล่างแสดงให้เห็นว่า VOL อยู่ในช่วง 0V – 0.5V และ VOH อยู่ในช่วง 2.7V – 5V สังเกตที่ VOH เห็นได้ว่าแรงดัน Output ของ TTL สามารถเป็นได้หมดในช่วงนี้ ส่วน Input มีค่า VIL อยู่ในช่วง 0V – 0.8V และ VIH อยู่ในช่วง 2V – 5V

แรงดัน Input จะต้องมีช่วงที่กว้างกว่า Output เพื่อคอนเฟิร์มว่าการสื่อสารระหว่าง IC ไม่มีปัญหา เพราะ Input สามารถรองรับแรงดัน Output ได้ทั้งหมด

อาจสงสัยว่าช่วงแรงดันตรงกลางที่ไม่ใช่ทั้ง High และ Low แรงดันจะเป็นยังไง คำตอบคือช่วงตรงกลางนี้เป็นช่วงที่ไม่สามารถคอนเฟิร์มได้ว่าแรงดันอยู่สถานะใด อาจเป็น High หรือ Low ก็ได้ทั้งคู่

CMOS Voltage Level

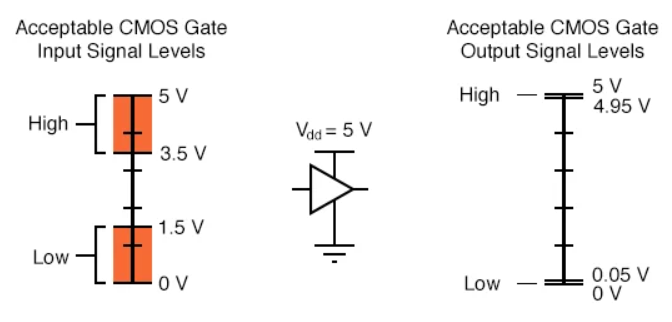

CMOS Output จะปล่อยแรงดันได้ดีมากซึ่งต่างจาก TTL ในรูปด้านล่างแสดงให้เห็นว่า VOL อยู่ในช่วง 0V – 0.05V และ VOH อยู่ในช่วง 4.95V – 5V จะเห็นได้ว่าแรงดันใกล้เคียง 5V และ 0V มาก ส่วน Input มีค่า VIL อยู่ในช่วง 0V – 1.5V และ VIH อยู่ในช่วง 3.5V – 5V

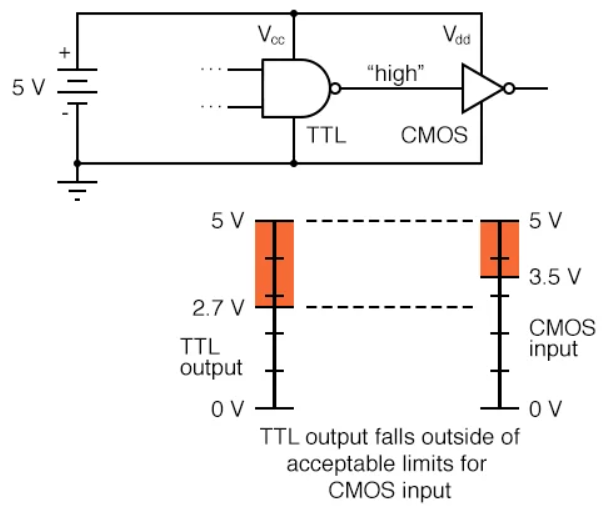

ฉะนั้นจะออกแบบให้ CMOS รับสัญญาณจาก TTL ดังรูปด้านล่างนี้ ก็จะทำให้วจรทำงานผิดพลาดได้ เนื่องจากช่วงแรงดัน Output ของ TTL นั้นกว้างเกินไป ทำให้มีช่องว่างที่ CMOS รับไม่ได้

Fan-out

Fan-out คือความสามารถในการขับกระแสของ IC ซึ่งถ้าไม่ตรวจสอบตรงนี้ก็อาจทำให้วงจรทำงานผิดพลาดได้เช่นกัน มาทำความรู้จักคำศัพท์ต่อไปนี้กัน

- Current Input High (IIH) : ช่วงกระแสที่ IC ต้องการขับเมื่อแรงดันเป็นสถานะ High

- Current Input Low (IIL) : ช่วงกระแสที่ IC ต้องการขับเมื่อแรงดันเป็นสถานะ Low

- Current Output High (IOH) : ช่วงกระแสที่ IC สามารถขับได้เมื่อแรงดันเป็นสถานะ High

- Current Output Low (IOL) : ช่วงกระแสที่ IC สามารถขับได้เมื่อแรงดันเป็นสถานะ Low

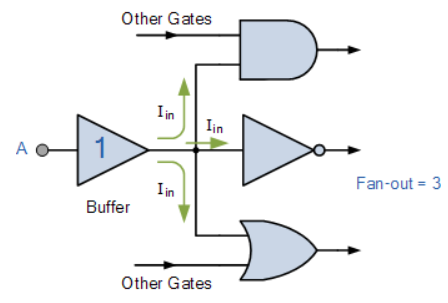

ตัวอย่างในรูปด้านล่าง มี Buffer#1 ขับกระแสจ่ายให้ Logic gate ตัวอื่นๆได้ 3 ตัว สมมติว่า IOH มีค่าเป็น 4mA และกระแส IIH ที่ Logic Gate ที่ทั้ง 3 ตัวต้องการรวมกันคือ 3mA วงจรนี้สามารถทำงานได้ไม่มีปัญหา (ตรวจสอบ Logic Voltage Level ผ่านแล้วนะ)

ตัวอย่างการอ่าน Datasheet

ในหัวข้อนี้จะยกเอาข้อมูลจาก Datasheet ของ ESP32 มาให้เห็นกัน ซึ่งมีข้อมูลที่ต้องการครบเลยในรูปด้านล่าง ESP32 นั้นใช้ไฟ 3.3V เพราะฉะนั้นแรงดัน VIL จะอยู่ในช่วง -0.3V – 0.825V, VIH จะอยู่ในช่วง 2.475V – 3.6V, VOL จะไม่เกิน 0.33V, VOH จะไม่ต่ำกว่า 2.64V ส่วนค่ากระแส IIL, IIH, IOL, IOH สามารถอ่านตามตารางได้ตรง ๆ เลย

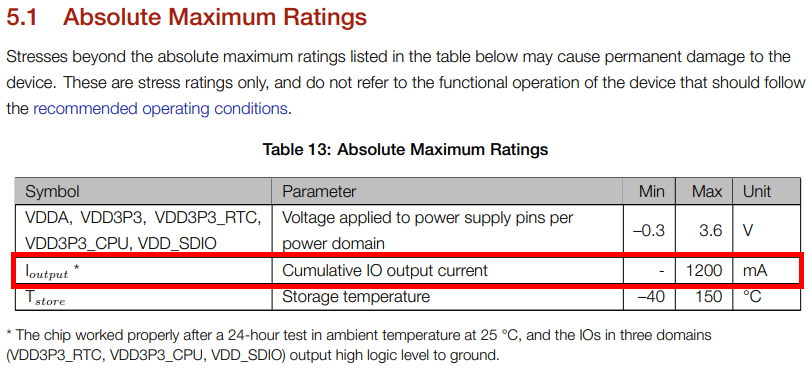

ข้อควรระวังสำหรับการขับกระแส Output เนื่องจาก ESP32 นั้นมีหลายพอร์ตที่เอาไว้ใช้งาน นอกจากตรวจสอบตารางข้างต้นแล้ว ยังต้องตรวจสอบผลรวมของกระแส Output ที่ใช้งานด้วยว่าเกินจากที่กำหนดหรือไม่ แสดงดังรูปด้านล่าง หมายความว่าผลรวมกระแสของ Output ทุกพอร์ตต้องไม่เกิน 1200mA ซึ่งจริงๆแล้วถ้าออกแบบวงจรไม่ได้ใช้ขับกระแสอะไรมาก เป็นไปได้ยากที่ผลรวมกระแสจะเกิน