ในบทความนี้จะมาแนะนำวิธีการสร้าง GPIO IP ขึ้นมาด้วยตัวเอง และ การเพิ่ม GPIO IP ที่สร้างขึ้นนี้เป็น IP ใน Platform Designer บน Quartus

โดยจะอธิบายข้อมูลเบื้องต้นเกี่ยวกับ GPIO และ Platform Designer ก่อนจะกล่าวถึงขั้นตอนการสร้าง

- GPIO ย่อมาจาก General Purpose Input/Output คือ ขา Input และ Output ใน Microcontroller หรือMicroprocessor ที่สามารถใช้ควบคุมหรือรับข้อมูลจากอุปกรณ์ภายนอกได้ โดย GPIO สามารถกำหนดให้เป็น Input/Output ก็ได้ สำหรับ Altera ได้มี IP สำหรับใช้ควบคุม GPIO โดยมีชื่อว่า PIO core แต่หากต้องการสร้างฟังก์ชั่นสำหรับการควบคุม GPIO เพิ่มเติม เช่น การสร้างสัญญาณ PWM ออกที่ GPIO ก็จำเป็นต้องสร้าง IP ของตัวเองขึ้นมาเพื่อนำไปใช้ในระบบด้วย Platform Designer

- Platform Designer คือ Software ของ Altera บน Quartus ที่เป็นเครื่องมือออกแบบระบบภายใน FPGA ที่ประกอบไปด้วย IP ต่างๆ ซึ่งจะทำการสร้าง logic สำหรับ Bus ภายในให้โดยอัตโนมัติ และแต่ละ IP ก็จะมีข้อกำหนดสำหรับ Interfaces เหมือนกันเพื่อให้สามารถสื่อสารกันได้ภายใต้ Bus ที่ระบบสร้างขึ้นมาให้

ขั้นตอนการเขียนไฟล์ VHDL เพื่อสร้างเป็น GPIO IP

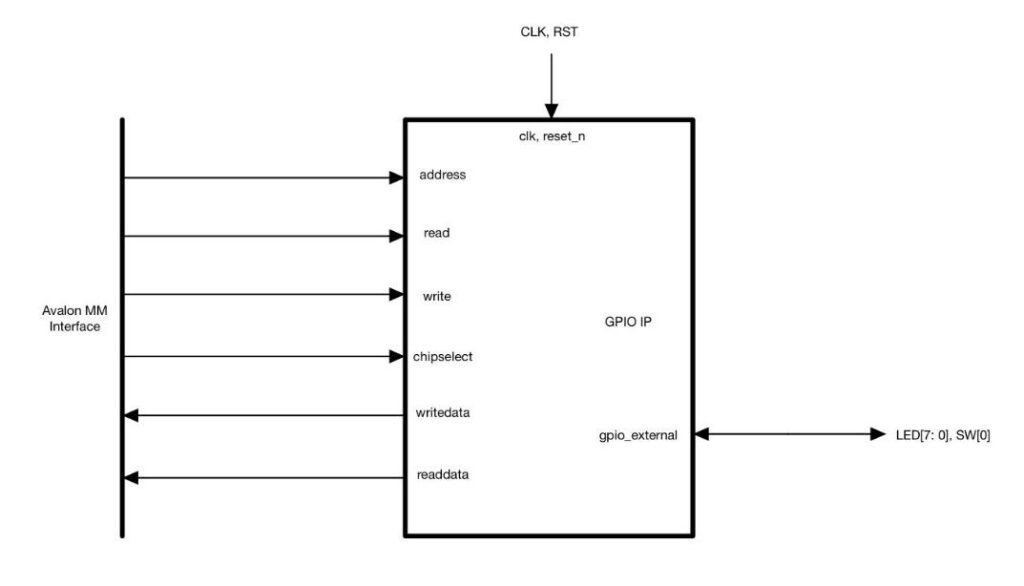

- ก่อนอื่นต้องออกแบบ GPIO IP ที่จะสร้างโดยกำหนดสัญญาณ Input/Output ทั้งหมด พร้อมทั้งวาด Block Diagram คร่าวๆ

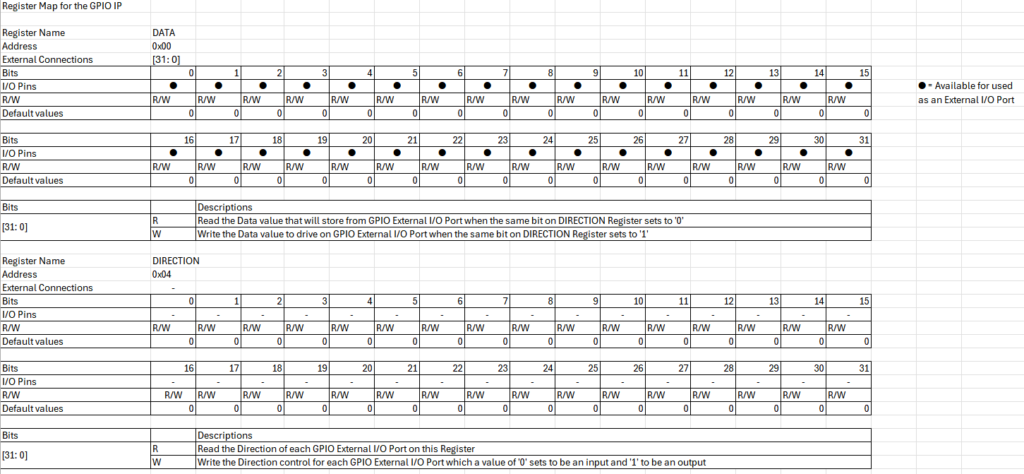

- ออกแบบการทำงานของ GPIO IP ในส่วนนี้อาจสร้างเป็น Register Map ขึ้นมาก็ได้

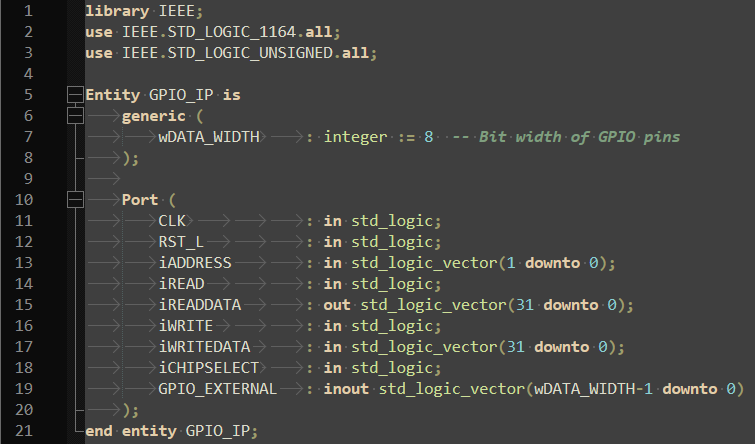

- เขียนไฟล์ VHDL โดยเริ่มจากส่วน Entity คือกำหนดสัญญาณ Input/Output ของ GPIO IP ที่จะสร้างขึ้นนี้

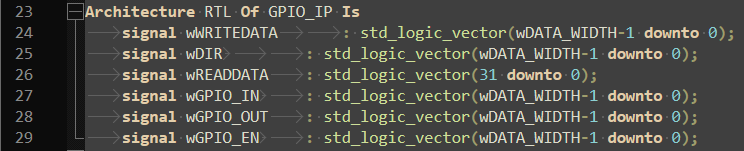

- ประกาศ Signals ต่างๆ ที่ต้องใช้ภายใน

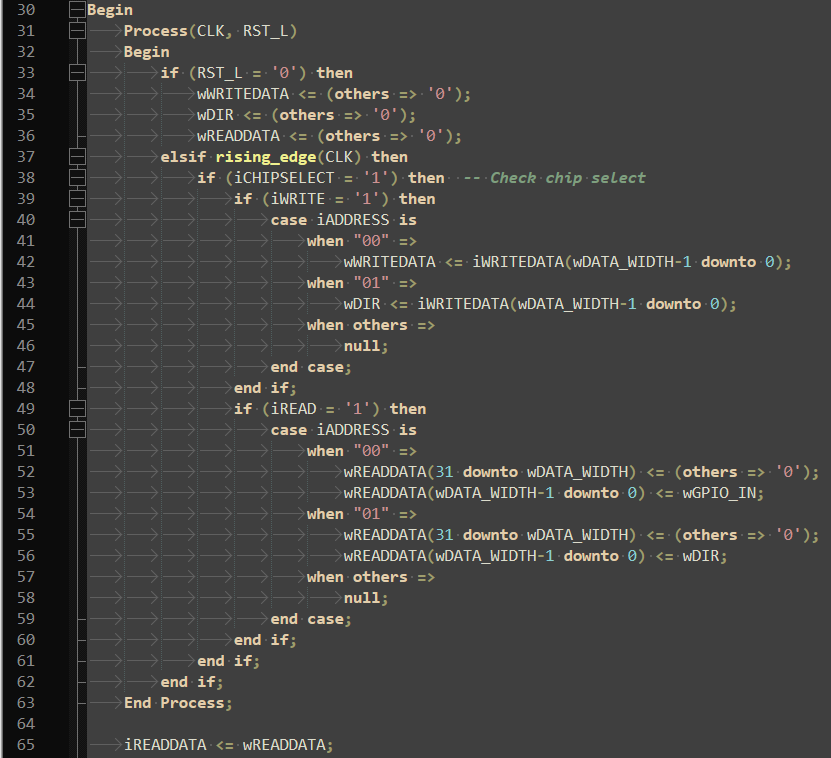

- Process การทำงานก็จะแบ่งเป็น Write กับ Read โดยจะมีการพิจารณา Address เพื่อเลือก Write/Read ระหว่าง DATA/DIRECTION ตามที่ได้ระบุไว้ใน Register Map

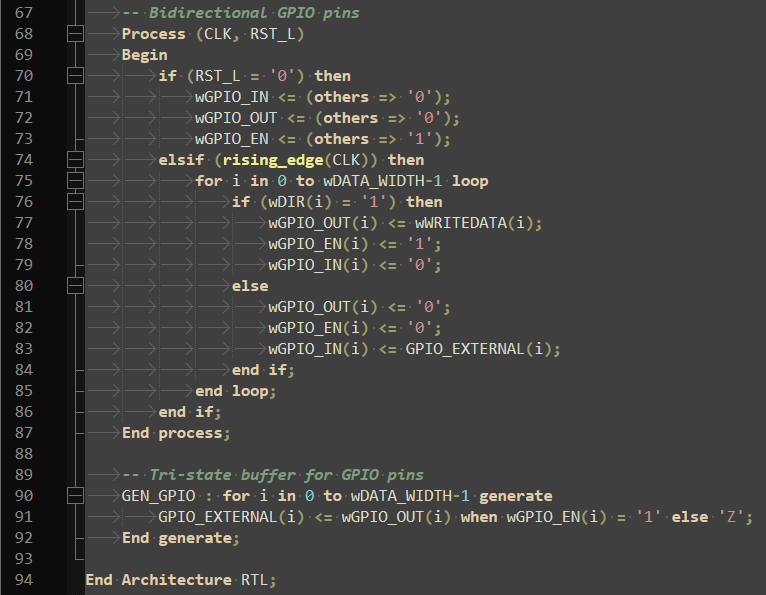

- สำหรับในบทความนี้จะทำการสร้าง GPIO IP แบบ BiDirection กล่าวคือสามารถกำหนดให้เป็น Port Input หรือ Output ได้จากค่าที่เขียนลงไปใน DIRECTION Register แต่จำเป็นต้องมี Tri-state buffer เพื่อไม่ให้เป็น Port หนึ่งเป็นทั้ง Input และ Output พร้อมกัน ซึ่งจะไม่สามารถทำงานได้

ขั้นตอนการเพิ่ม GPIO IP ที่สร้างขึ้นเป็น IP ใน Platform Designer บน Quartus

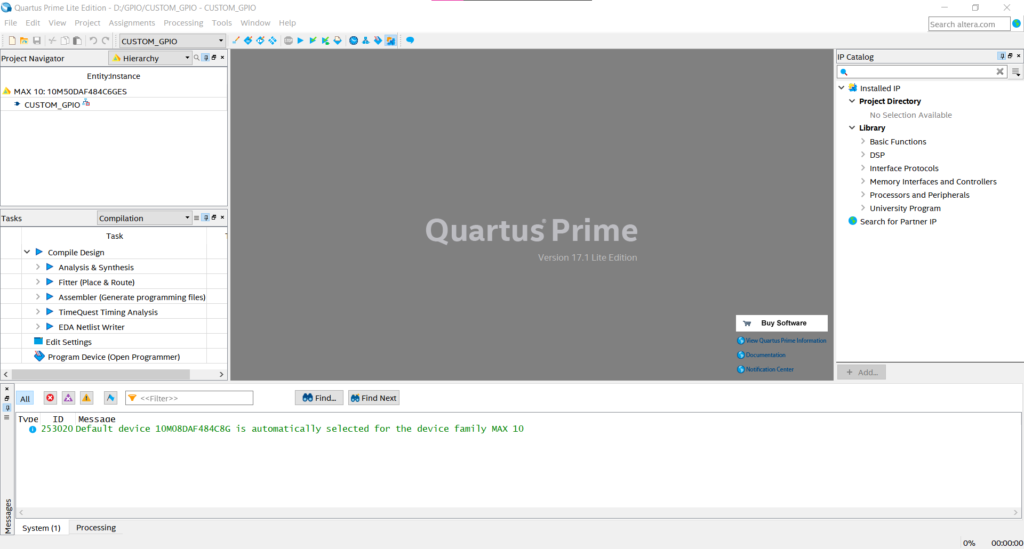

- สร้าง Project ขึ้นมาบน Quartus

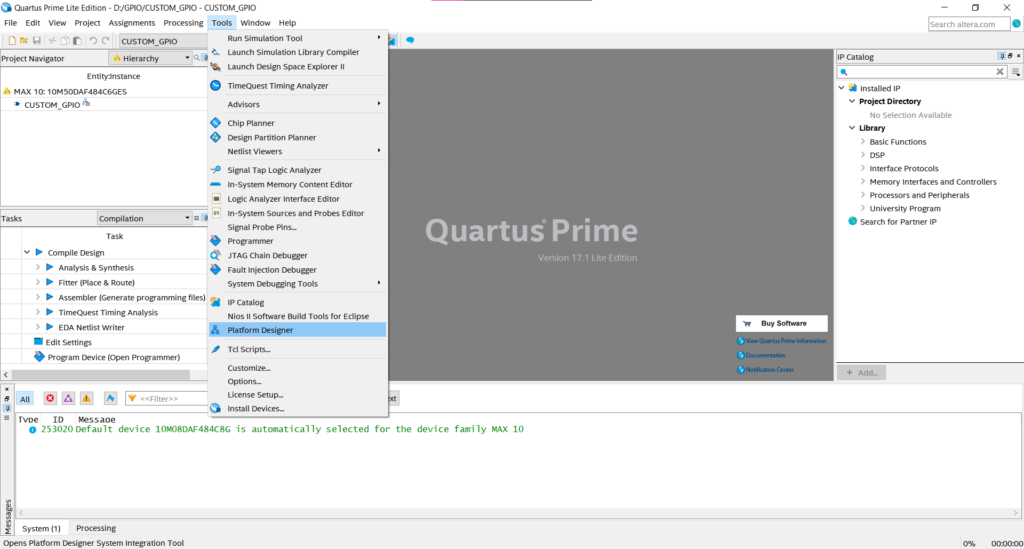

- เปิด Tools 🡪 Platform Designer

- เมื่อเปิดขึ้นมาแล้ว ให้เลือก New Component บนแท็บ IP Catalog ทางซ้าย

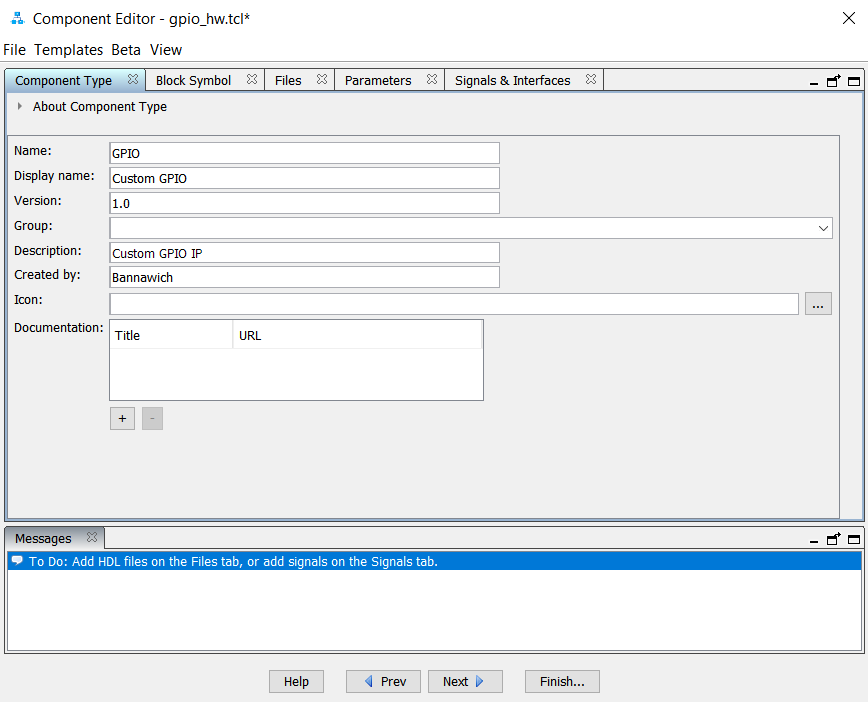

- จะปรากฏหน้าต่าง Component Editor ขึ้นมา โดยในแท็บ Component Type ให้ใส่ Name ( ชื่อที่จะปรากฏบนแท็บ System Contents และเป็นชื่อของ Component นี้หลังจาก Generate ระบบนี้เป็นไฟล์ HDL ) และ Display name ( ชื่อที่จะปรากฏบนแท็บ IP Catalog ) ส่วนรายละเอียดที่เหลือเป็น Optional

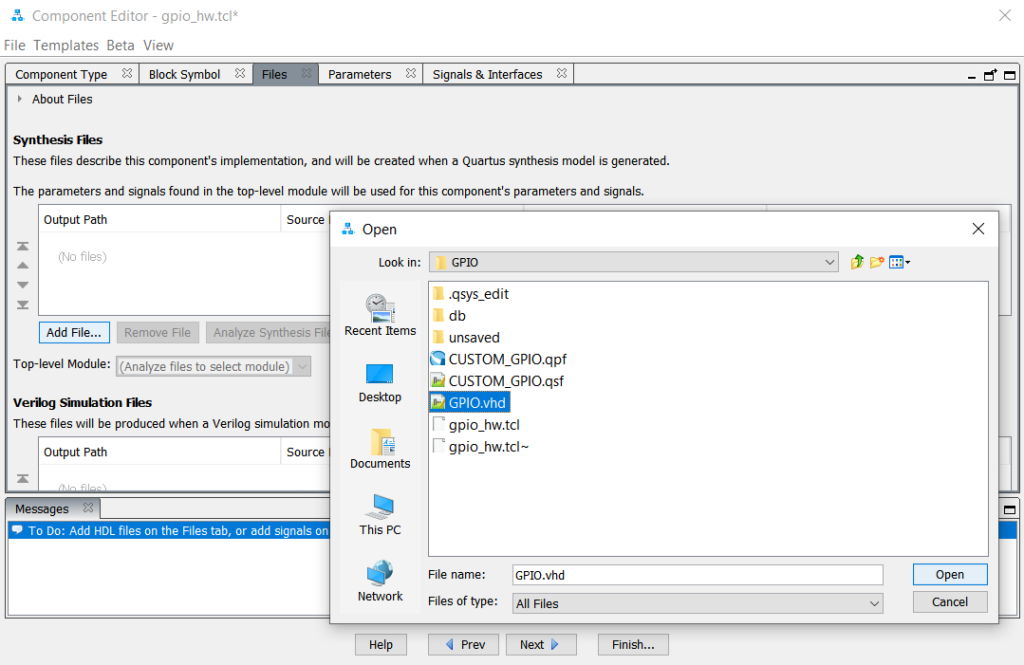

- ไปที่แท็บ Files บนหน้าต่าง Component Editor จากนั้นกด Add File ที่ Synthesis Files แล้วเลือกไฟล์ VHDL ที่ได้เขียนไว้เพื่อสร้าง GPIO IP เสร็จแล้วกด Open

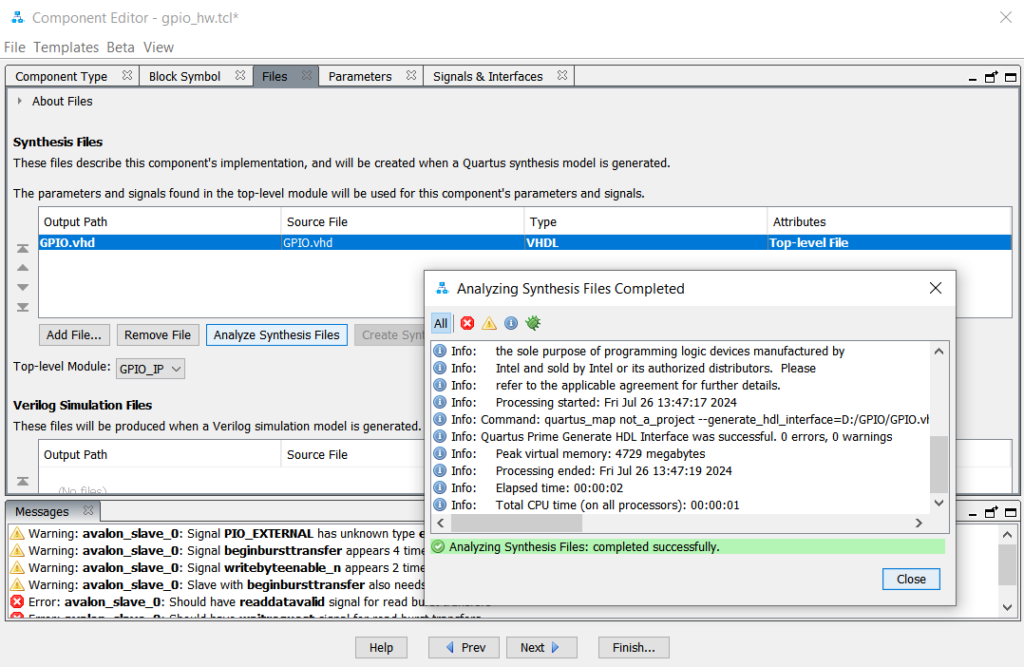

- กด Analyze Synthesis Files โดยถ้าไม่มี Errors ในไฟล์ VHDL ที่ Add เข้ามาก็จะขึ้นหน้าต่าง Analyzing Synthesis Files Completed จากนั้นกด Close เพื่อปิดหน้าต่างดังกล่าว ( หากมีการ Add Files มากกว่า 1 Files จำเป็นต้องกำหนด Top-level File ที่ Attributes ให้ถูกต้อง )

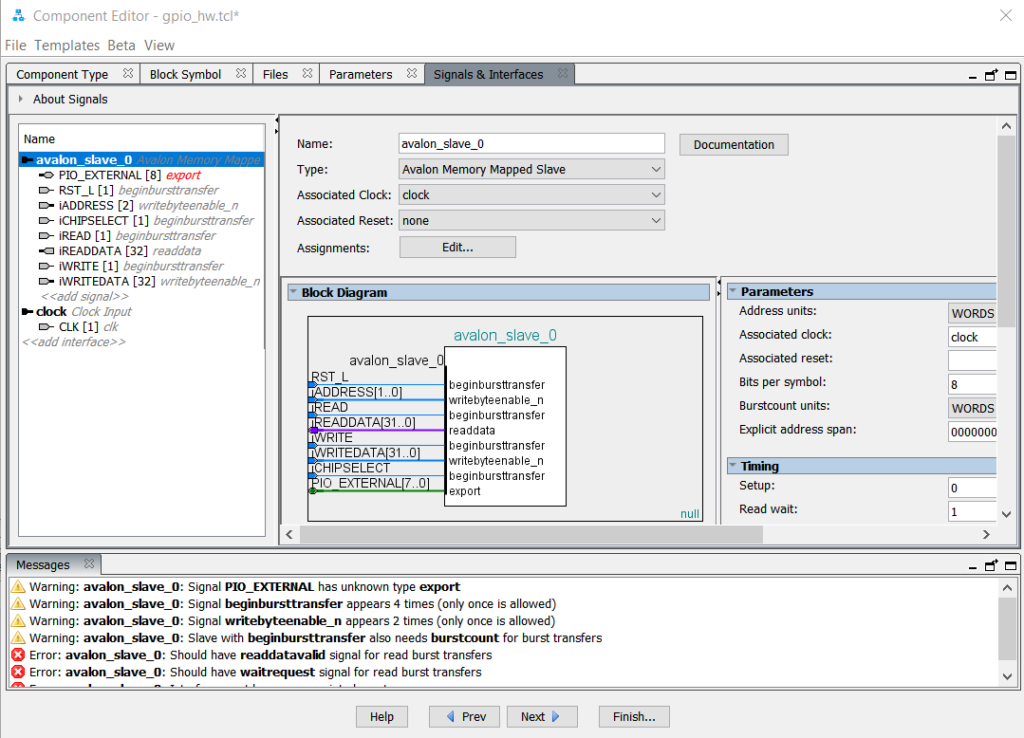

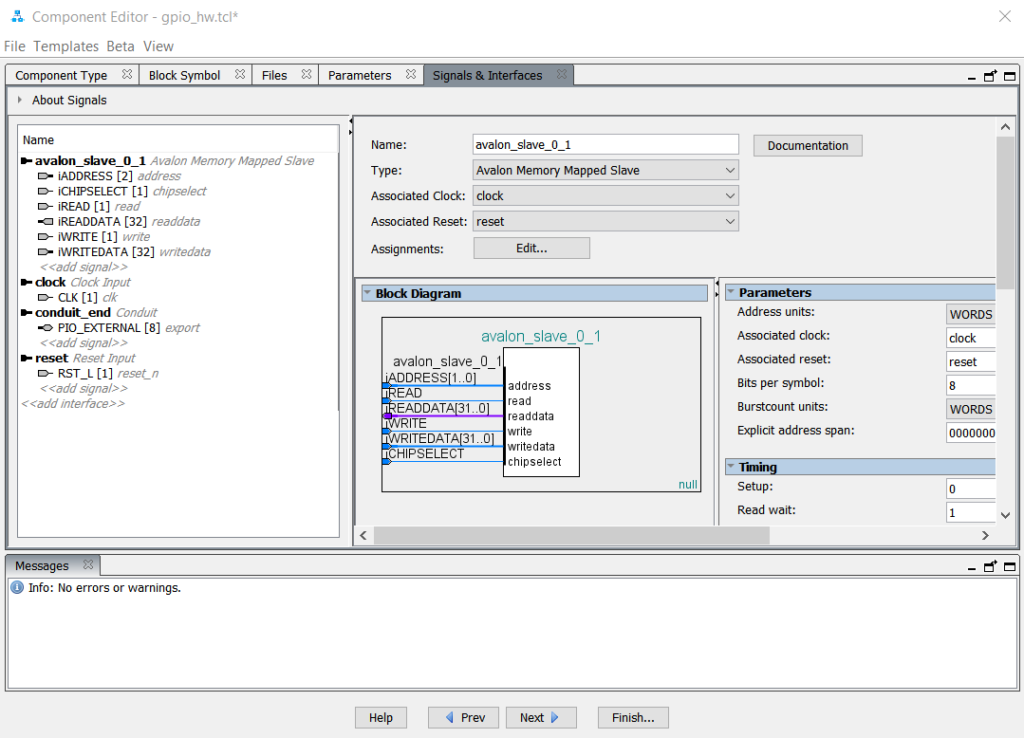

- ไปที่แท็บ Signals & Interfaces ในส่วนนี้จะต้องตรวจสอบและตั้งค่า Interfaces และ Signal ใน Interfaces นั้นๆ ให้ถูกต้อง

- ตั้งค่า Signals & Interfaces ซึ่งตามที่ได้ออกแบบไว้จะมี Interfaces 4 ส่วน ได้แก่ Clock Input, Reset Input, Avalon Memory Mapped Slave, Conduit สำหรับ Signals ต่างๆ ในแต่ละ Interfaces แสดงในภาพ เสร็จแล้วตรวจสอบแท็บ Messages ด้านล่างว่าไม่มี Errors ค่อยกด Finish

- GPIO IP ที่เราสร้างก็จะแสดงในแท็บ IP Catalog

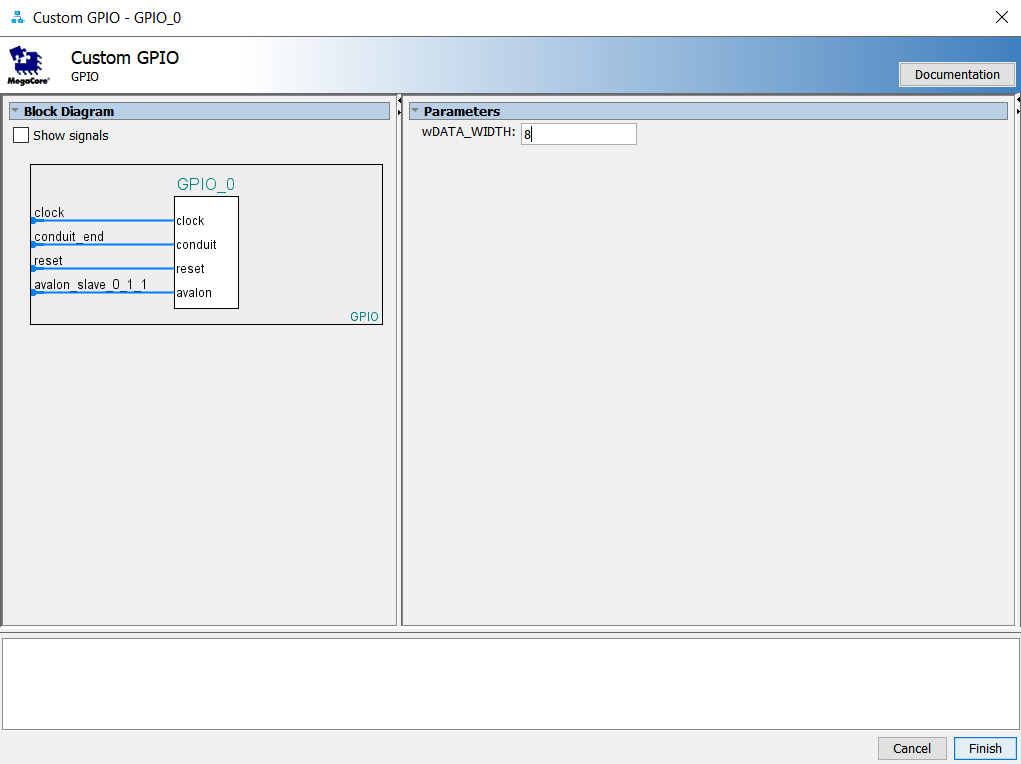

- Double-Click เพื่อ Add เข้ามาในระบบ โดยใส่ค่า Parameters ตามที่ต้องการก่อน เสร็จแล้วกด Finish

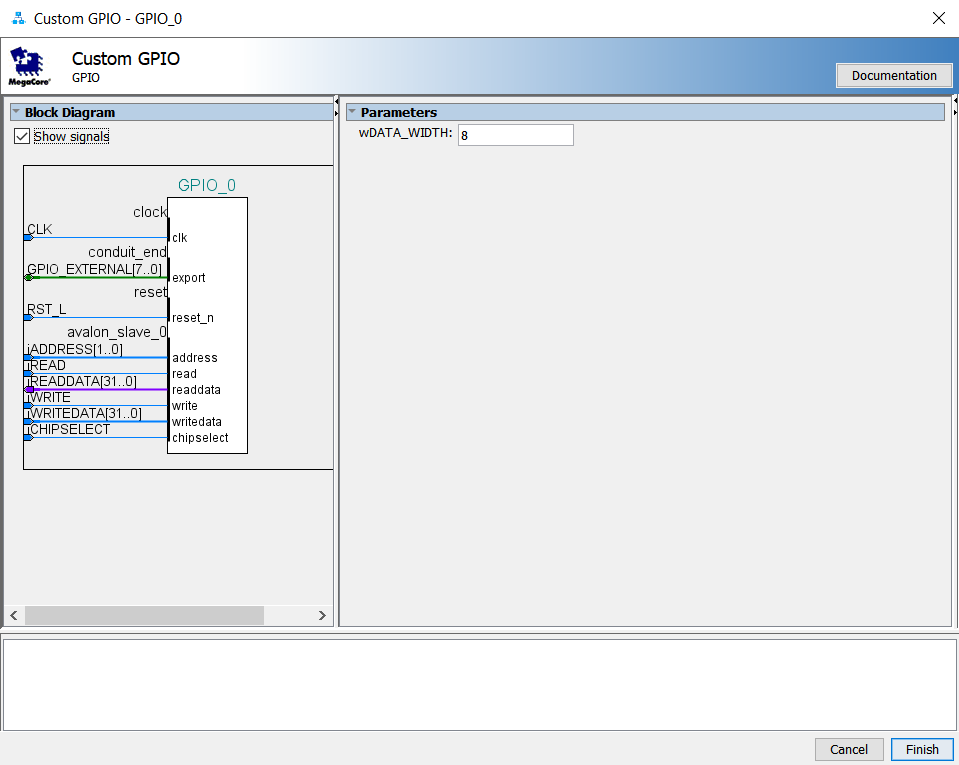

- สามารถกด Show signals เพื่อดูสัญญาณทั้งหมดได้ ซึ่งจะพบว่ามีลักษณะเหมือนกับ Block Diagram ที่ได้วาดไว้

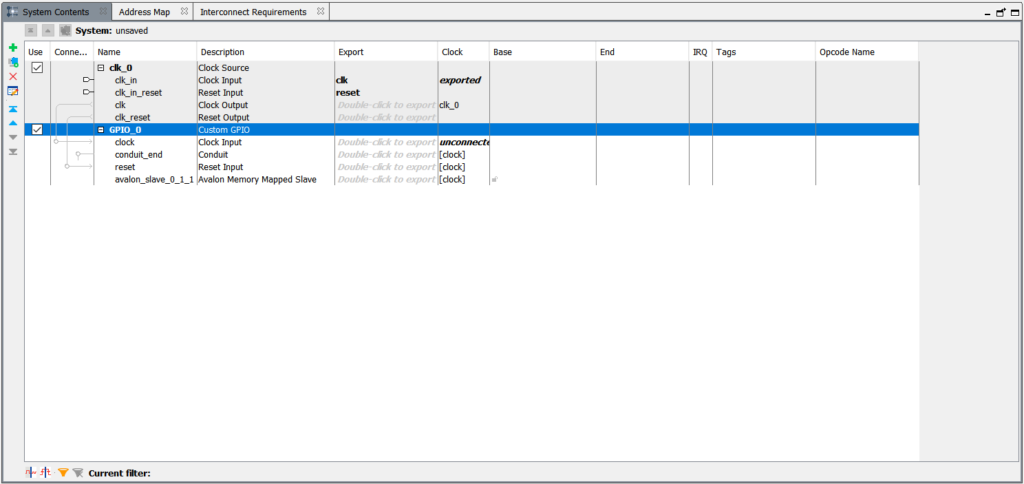

- GPIO IP ของเราก็จะปรากฏบนแท็บ Systems Contents เพื่อให้สามารถเชื่อมต่อสัญญาณกับ Components อื่นๆ ในระบบนี้ได้ ถือเป็นอันเสร็จสิ้นการเพิ่ม GPIO IP ที่สร้างขึ้นเองเป็น IP บน Platform Designer

จบไปแล้วสำหรับบทความเรื่องวิธีการสร้าง GPIO IP เป็น IP ใน Platform Designer หวังว่าบทความนี้จะเป็นประโยชน์ต่อผู้ที่สนใจไม่มากก็น้อยนะครับ หากมีข้อสงสัย หรือ ข้อเสนอแนะเพิ่มเติมสามารถติดต่อได้ที่ Facebook : Bannawich Horie ขอบคุณครับ