บทความนี้จะกล่าวถึงความสามารถในการบูต Nios II รูปแบบต่างๆของ MAX10 ก่อนจะเข้าเนื้อหาผู้เขียนขออธิบายความสามารถคร่าวๆเกี่ยวกับ MAX 10 ก่อน

MAX 10 คืออะไร?

MAX 10 เป็น FPGA ตระกูลหนึ่งของบริษัท Intel ที่มี Configuration memory ในตัว เมื่อปิดไฟหรือเกิดเหตุการณ์ไฟตก FPGA Image จะยังคงอยู่ ไม่หายไปเหมือน FPGA ทั่วไป ทำให้เวลาใช้งาน ไม่มีความจำเป็นต้องต่อ Configuration memory จากภายนอก และเวลาที่ใช้ในการบูตแค่หลัก ms เพียงเท่านั้น มี Soft Core CPU คือ Nios II ให้ใช้งานได้ฟรี สามารถเชื่อมต่อกับ External Memory ได้แก่ DDR3 SDRAM / DDR3L SDRAM / DDR2 SDRAM / LPDR2 DRRAM

ผู้เขียนแนะนำให้ผู้อ่านได้ศึกษาเกี่ยวกับ พื้นฐานการออกแบบ Nios II ก่อนจะเข้าสู่เนื้อหาด้านล่างนี้

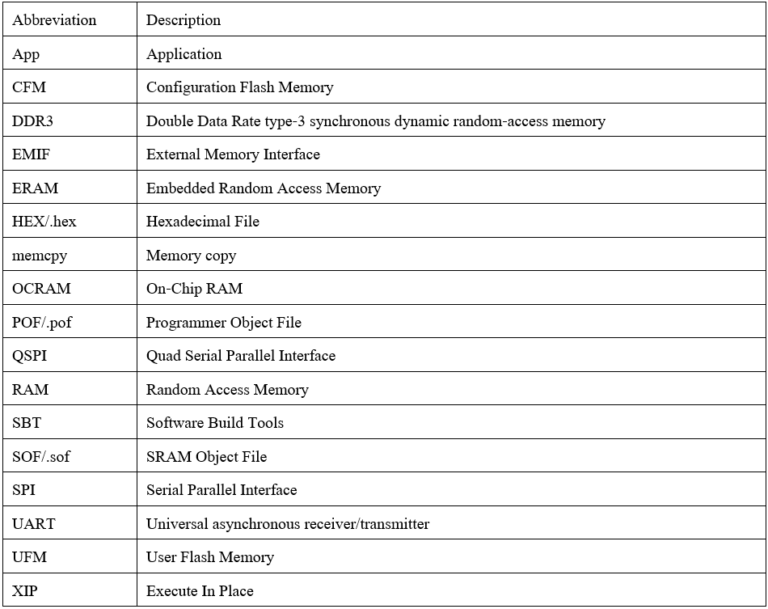

คำศัพท์ สำหรับเนื้อหานี้

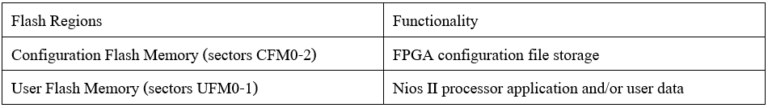

MAX 10 FPGA On-chip Flash

ประกอบไปด้วยส่วนที่ใช้สำหรับเก็บ FPGA Config ( CFM ) และ ส่วนที่เก็บ Nios II Application ( UFM )

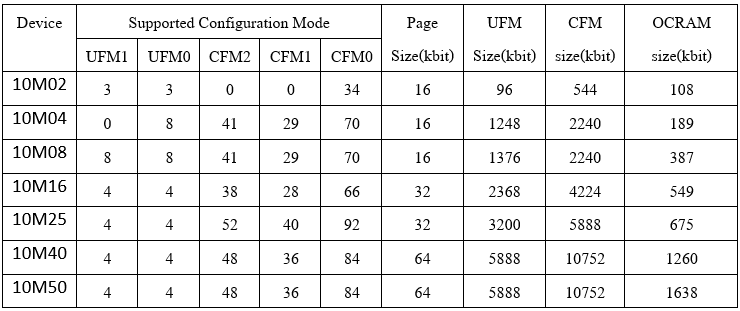

แสดงในตารางด้านล่างนี้

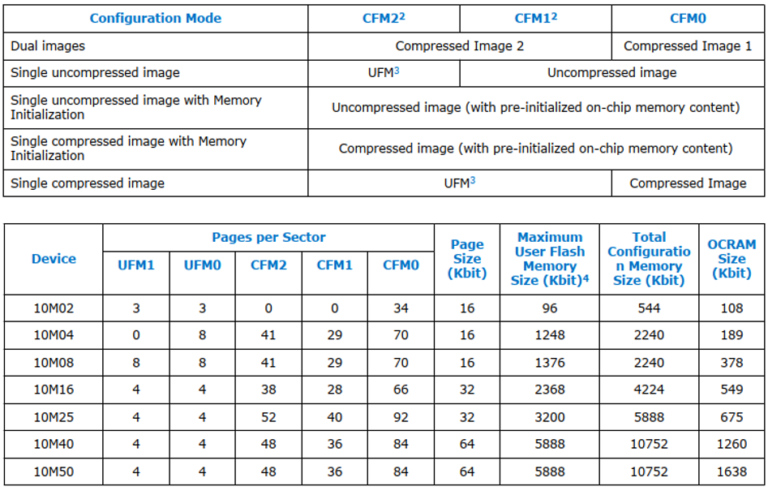

ในแต่ละ Config โหมด จะใช้ตำแหน่งบน Sector ของ CFM ไม่เหมือนกันแสดงในตารางด้านล่างนี้

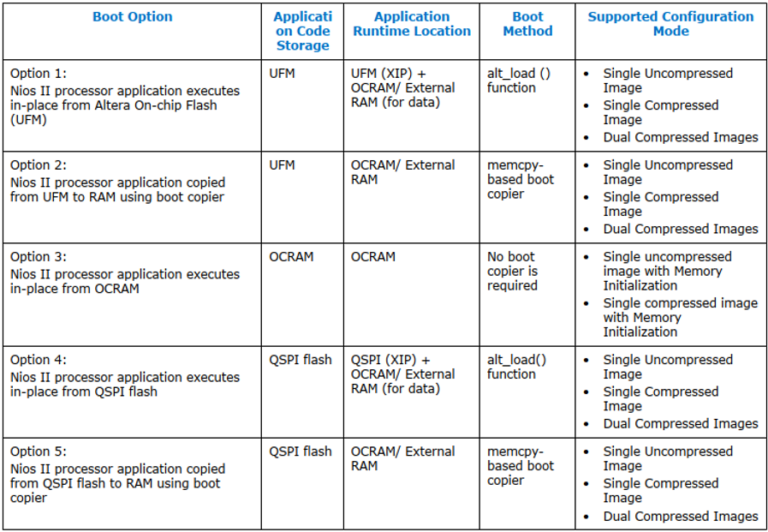

Nios II Processor Boot Options แต่ละ Column มีรายละเอียดดังต่อไปนี้

- Boot Option หมายถึง ตัวเลือกของการบูต มีทั้งหมด 5 รูปแบบ

- Application Code Storage หมายถึง พื้นที่สำหรับการจัดเก็บ Nios II แอพพลิเคชั่น

- Application Runtime Location หมายถึง พื้นทำงานของแอพพลิเคชั่น

- Boot Method หมายถึง ฟังก์ชันการบูต

- Support Configuration Mode หมายถึง โหมด CFM ที่รองรับ จะต้องเข้าไปตั้งค่าใน Configuration mode ใน Quartus II ให้ตรงกับ QSYS ด้วย

NIOS II PROCESSOR BOOT OPTIONS

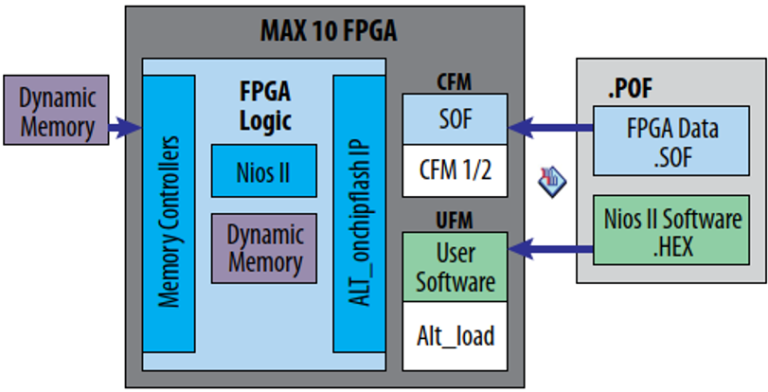

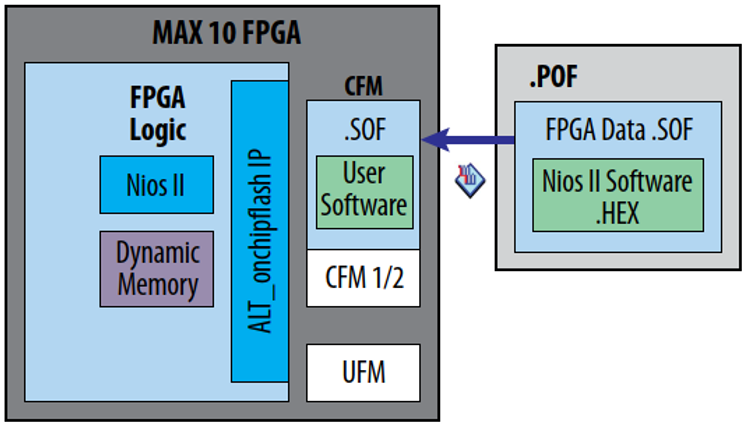

Boot Option 1: Nios II Processor Application Executes in-place from Altera On-chip Flash (UFM)

จะเป็นการเก็บ Software ไว้ที่ UFM และ รัน APP บน UFM(XIP)+OCRAM หรือ External RAM โดยจะต้องกำหนดพื้นที่ของ UFM ให้มีขนาดใหญ่กว่าขนาดของ Software ซึ่งขนาดของ UFM จะมีขนาดตาม Part Number ของ FPGA ที่ใช้งาน ฟังก์ชั่น alt_load() จะทำการ copy ข้อมูลที่สามารถอ่านและเขียนได้พวก .rodata, .rwdata, exceptions จาก UFM ไปยัง OCRAM/RAM ส่วนข้อมูลที่อ่านได้อย่างเดียวพวก .text จะถูกเก็บไว้บน UFM โดยสามารถกำหนดได้ที่ BSP setting ที่อยู่ใน Nios II Software Build Tools ถ้าหากต้องการ Debug ในระดับ source-level ผู้ใช้จะต้องใช้ hardware break-point สำหรับการ Debug เนื่องจาก UFM ไม่รองรับ random memory access ( hardware break-point คือ Debug ในระดับ Register )

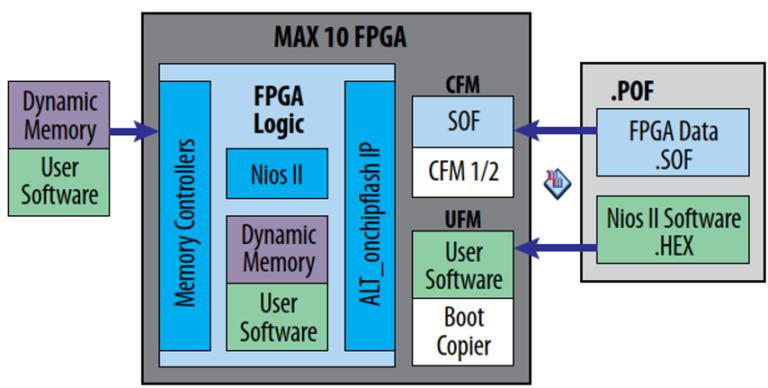

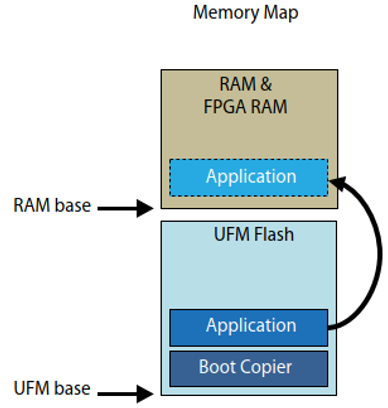

Boot Option 2: Nios II Processor Application Copied from UFM to RAM using Boot Copier

ทาง Intel ได้แนะนำให้ใช้ Boot Option นี้ เนื่องจากสามารถ Debug ในระดับ source-level ( Soft Break-Point ) ทำการการพัฒนามีประสิทธิภาพสูง จะเป็นการเก็บ Software ไว้ที่ UFM และรันแอพพลิเคชั่นทั้งหมดบน OCRAM หรือ External RAM ซึ่งจะต้องกำหนดพื้นที่ของ UFM ให้มีขนาดใหญ่กว่าขนาดของ Software โดย ฟังก์ชั่น memcpy-based boot copier จะทำการ copy software application image จาก UFM ไปสู่ OCRAM/RAM สำหรับ memcpy-based boot copier ฟังก์ชั่น จะมีแค่ Boot Option 2 และ Boot Option 5 เท่านั้น

Boot Option 3: Nios II Processor Application Executes in-place from OCRAM

CFM จะทำการ Initialized ในขณะที่ FPGA กำลัง Config อยู่ ทำให้หลังจาก reset แล้ว Nios II อยู่ในสภาพพร้อมทำงาน ซึ่ง Boot Option นี้ จะไม่รองรับการทำงานแบบ Dual Boot ( มี 2 Image ใน FPGA 1 ตัว ) Software ทั้งหมดจะถูกรันบน OCRAM เท่านั้น ในขั้นตอนการออกแบบ จะต้อง check Initialize flash content ใน RAM หรือ ROM IP หากมีการแก้ไข Software ใหม่ จะต้องทำการ Compile FPGA ทุกครั้ง ไม่เหมาะสำหรับการ Debug เพราะใช้เวลา Compile ค่อนข้างนาน

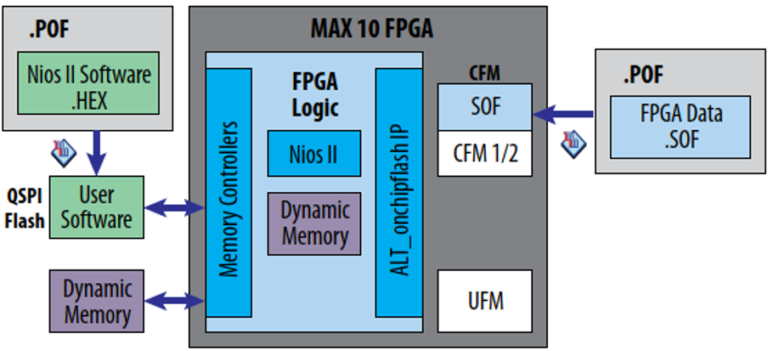

Boot Option 4: Nios II Processor Application Executes in-place from QSPI Flash

สำหรับ Boot Option นี้ จะมีลักษณะคล้ายคลึงกับ Boot Option 1 ต่างกันที่พื้นที่จัดเก็บ Software โดยจะเก็บไว้ที่ QSPI Flash โดยฟังก์ชั่น alt_load() จะทำการ copy ข้อมูลที่สามารถอ่านและเขียนได้พวก .rodata, .rwdata, exceptions จาก Boot memory ไปสู่ OCRAM/RAM ส่วนข้อมูลที่อ่านได้อย่างเดียวพวก .text จะถูกเก็บไว้บน QSPI Flash

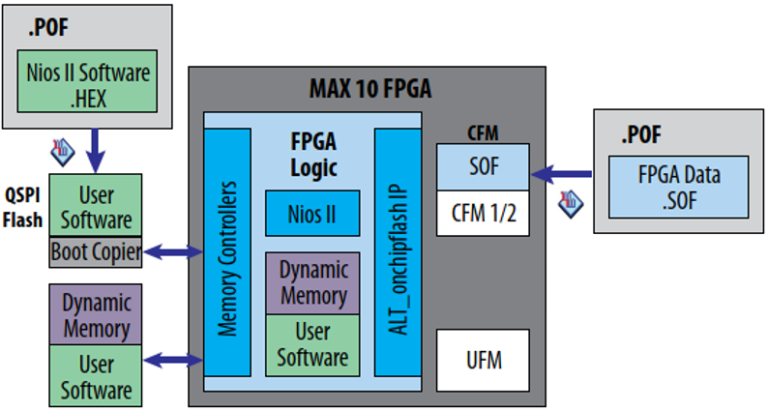

Boot Option 5: Nios II Processor Application Copied from QSPI Flash to RAM Using Boot Copier

สำหรับ Boot Option นี้ จะมีลักษณะคล้ายคลึงกับ Boot Option 2 ต่างกันที่พื้นที่จัดเก็บ Software โดยจะเก็บไว้ที่ QSPI Flash โดยฟังก์ชั่น memcpy-based boot copier จะทำการ copy software application image จาก QSPI Flash ไปสู่ OCRAM/RAM

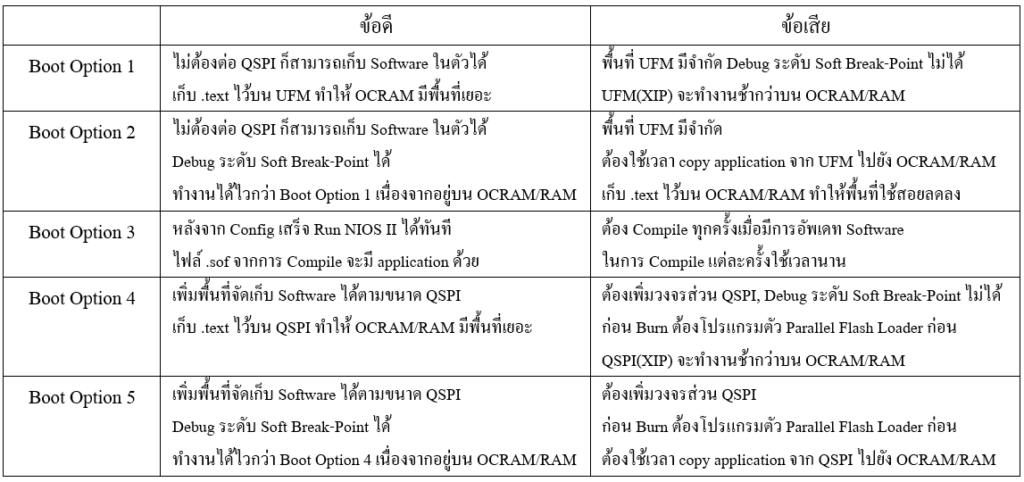

ข้อดีข้อเสียแต่ละ Boot Option

สำหรับในเนื้อหานี้ ผู้เขียนขอสรุปทุก Boot Option ไว้ในเนื้อหาด้านล่างนี้เลย

1. การตั้งค่า Nios II IP

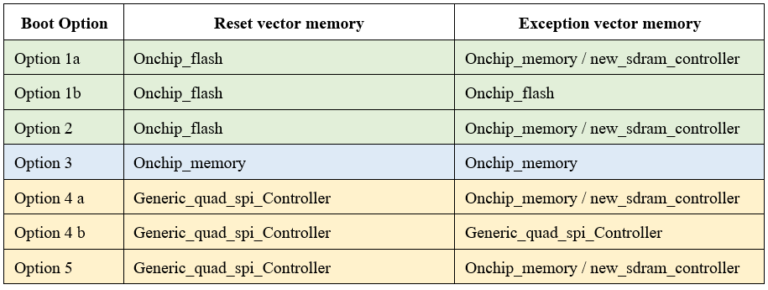

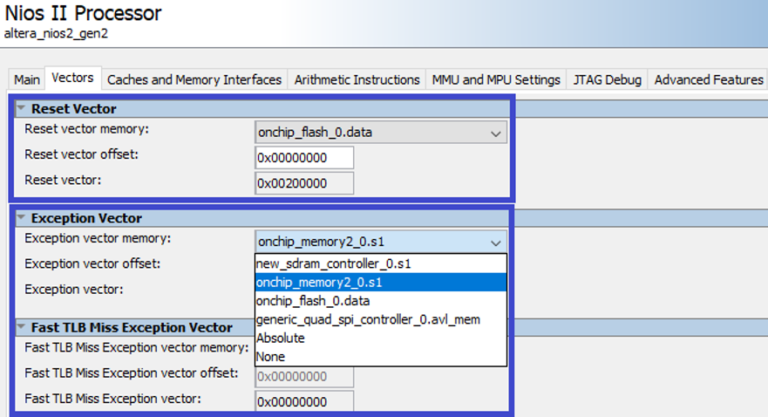

สำหรับการกำหนด Exception vector memory ของ Boot Option 1 สามารถกำหนดได้ 2 รูปแบบ

โดยรูปแบบ 1a กระบวนการ interrupt จะสามารถทำงานได้ไวกว่า 1b

เช่นเดียวกัน รูปแบบ 4a กระบวนการ interrupt จะสามารถทำงานได้ไวกว่า 4b

ขั้นตอนการออกแบบ QSYS สำหรับ แต่ละ Boot Option

สำหรับในเนื้อหานี้ ผู้เขียนขอสรุปทุก Boot Option ไว้ในเนื้อหาด้านล่างนี้เลย

1. การตั้งค่า Nios II IP

สำหรับการกำหนด Exception vector memory ของ Boot Option 1 สามารถกำหนดได้ 2 รูปแบบ

โดยรูปแบบ 1a กระบวนการ interrupt จะสามารถทำงานได้ไวกว่า 1b

เช่นเดียวกัน รูปแบบ 4a กระบวนการ interrupt จะสามารถทำงานได้ไวกว่า 4b

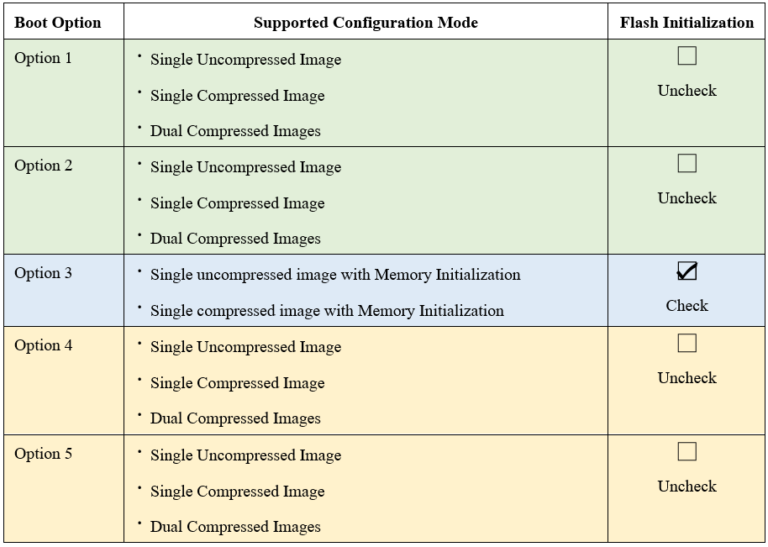

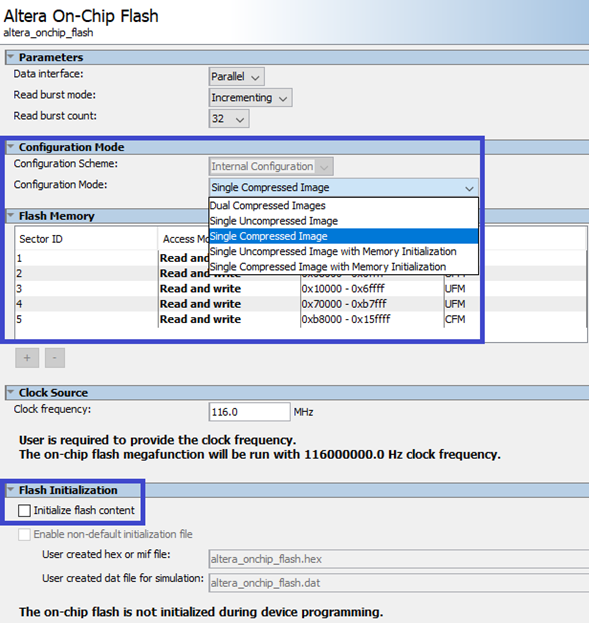

2. การตั้งค่า On-Chip Flash IP

สำหรับการกำหนด Configuration Mode แต่ละ Boot Option สามารถเลือกได้ว่าจะ Uncompressed Image หรือจะ Compressed Image ก็ได้ สำหรับ Boot Option 3 จะต้องทำการ Check ที่ Memory Initialization ด้วย

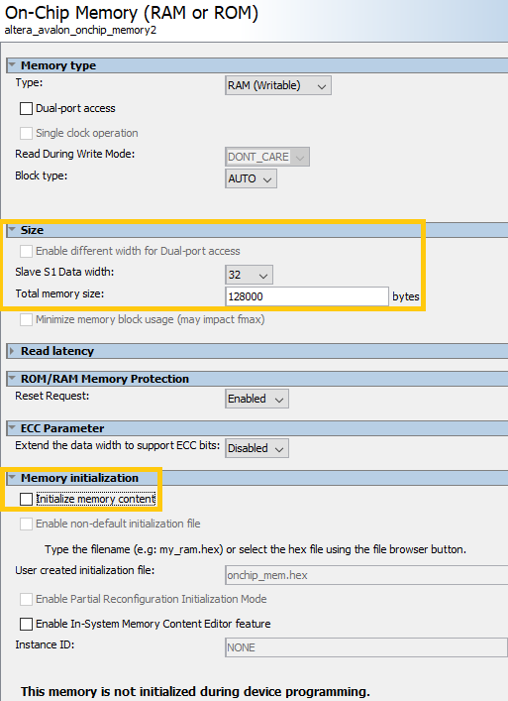

3. การตั้งค่า On-Chip Memory

สำหรับการกำหนด On-Chip Memory สามารถกำหนดขนาดได้ โดยต้องสัมพันธ์กับขนาดของ FPGA ที่ใช้ สำหรับ Boot Option 3 จะต้องทำการ Check ที่ Memory Initialization ด้วย

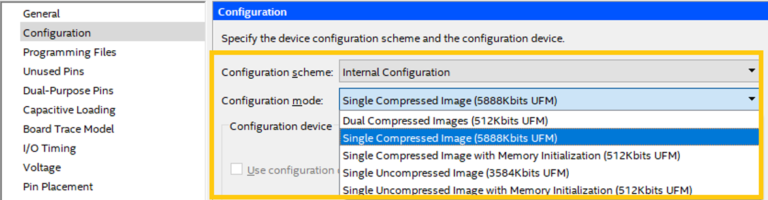

4. การตั้งค่า Quartus II

สำหรับการตั้งค่า Configuration mode บน Quartus II สามารถกำหนดได้ โดยเข้าไปที่ Quartus II software, click on Assignment -> Device -> Device and Pin Options -> Configuration. ตามภาพด้านล่างนี้ โดยจะต้องสัมพันธ์กับ ข้อ 2 ( การตั้งค่า On-Chip Flash IP )